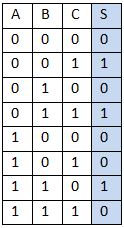

Si habéis decidido saltaros la introducción y habéis llegado hasta aquí, supongo que ya sabréis de qué va la cosa. Para el resto, como dije en dicho apartado, una vez tenemos el circuito, cuando lo vamos a montar, es decir, a la hora de utilizarlos en la realidad, utilizamos un circuito integrado que tiene unas características propias. Dichas características son otra excusa para darnos dolor de cabeza e introducir éste tema.

En primer lugar veremos que hay dos familias muy fácilmente distinguibles de integrados: TTL y CMOS. Como su nombre indica, la CMOS utiliza transistores tecnología MOS (MOSFET), y la TTL utiliza transistores BJT. Y ésto las hace diferentes.

Vamos a ver la nomenclatura de dichos integrados:

- 74: Estándar TTL

- 40 o 140: Estándar CMOS

- 74S: TTL Schottky

- 74L: TTL baja potencia

- 74LS: TTL baja potencia Schottky (Ésta es la más usada)

- 74H: TTL alta velocidad

- 74AS: TTL Schottky avanzada

- 74C: CMOS compatible con el patillaje de las TTL

- 74HC: CMOS alta velocidad (Más usada, actualmente más que la TTL)

- 74HCT: CMOS alta velocidad compatible con patillaje y tensiones de TTL

La familia 74HCT es muy importante hoy en día para reemplazar antiguos TTL o como compatibilidad con otros integrados de ésta tecnología, ya que tienen la misma distribución de patillas y semejantes características.

Características de Entrada / Salida

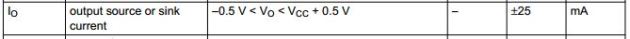

Ahora vamos a ver cómo sería una puerta inversora de tecnología TTL por dentro:

Como veis la entrada está conformada por un transistor puesto al revés, un transistor especial que se comporta como dos diodos, uno mirando hacia la base de Q2 y otro mirando hacia la entrada. Si ponemos la entrada a 0, la corriente va de VCC por la base hasta la entrada, drenando la corriente de la base de Q2 y poniéndolo en corte, de forma que a la salida tenemos un 1. Si ponemos la entrada a 1, la corriente no tiene otra que ir hacia la base de Q2 y polarizarlo en saturación, así que en la salida habrá un 0.

Por ésta cuestión es que si dejamos una patilla de entrada TTL al aire (no conectada a VCC, a tierra, a ningún sitio con referencia), se toma como si hubiese un 1, porque la corriente no puede fluir a través del diodo, que está ahí por protección.

Muy importante: patilla de entrada TTL al aire = 1. Si se recuerda ésta regla, se pueden simplificar bastante algunos diseños en el futuro.

Y ahora observemos una puerta inversora CMOS:

Es muy importante que la entrada de una puerta CMOS siempre esté conectada a algo, ya sea HIGH o LOW, si no, tendremos un estado indeterminado.

Es muy importante que la entrada de una puerta CMOS siempre esté conectada a algo, ya sea HIGH o LOW, si no, tendremos un estado indeterminado.

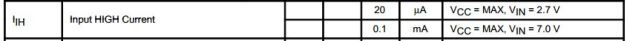

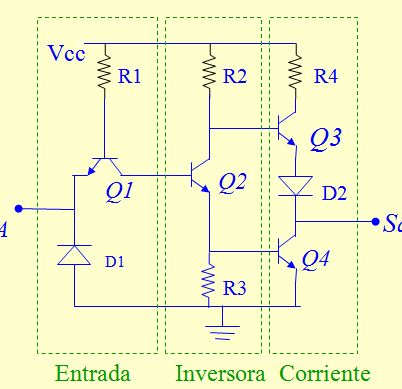

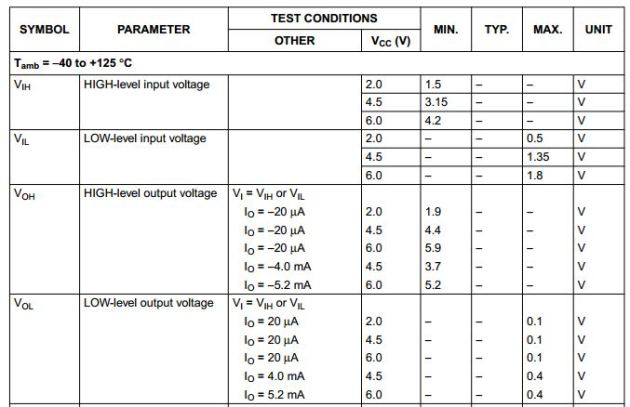

Aquí no es necesario resitencias ni nada… Bueno, ésto se debe al control por tensión de las puertas, supuestamente su impedancia de puerta es infinita, por lo tanto no habría corriente de entrada. Vale, ésto es falso, pero si comparamos la corriente de polarización entre una TTL y una CMOS (74LS04 y 74HC04):

Vemos que la CMOS tiene una corriente enana en comparación a la TTL. De 0.1uA (25ºC) a entre 20 y 100uA, hay bastante.

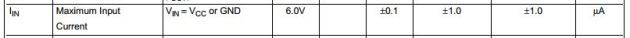

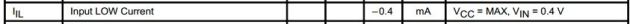

Otra cosa que se puede ver en la datasheet es la corriente a entrada LOW, es decir, cuando pongamos la entrada a masa (0), va a salir una corriente desde dicha entrada que polariza al transistor, por éso se expresa en negativo:

Vemos un máximo de 0.4 mA en la TTL ¿Y en la CMOS? La diferencia es tan poca que, si os fijáis, ya viene dada en la tabla de antes (la datasheet no especifica Input HIGH o Input LOW para CMOS, sólo Input Current).

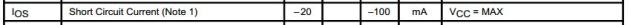

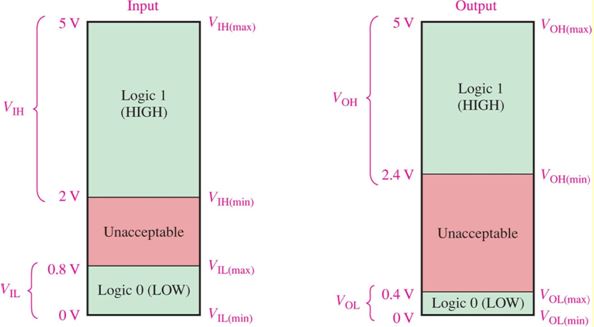

También a la salida tenemos unas especificaciones diferentes de corriente:

Como veis la TTL es capaz de entregar más corriente, sin embargo, debido a la corriente que necesita de entrada, no se pueden poner tantas puertas TTL en paralelo detrás de otra como si se tratase de CMOS. A ésto lo llamamos cargabilidad y va en número de puertas. Dados éstos datos podríamos poner unas 50 TLL o unas 200 CMOS.

Como el diseño TTL que hemos visto al principio otorgaba todavía menos corriente, se inventaron la salida totem-pole, que se basa en otra configuración de transistores añadida para aumentar la corriente de salida. Ésta configuración, creo, viene dada ya en todos los integrados. Los CMOS no la necesitan, pero se usan si son HCT para adaptar mejor.

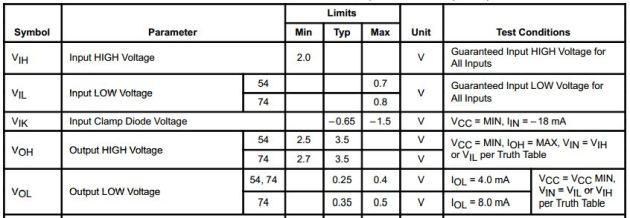

Pero ahora vamos a meternos en el tortuoso mundo de los niveles de entrada salida en tensión.

Éstos niveles también nos los da el fabricante y nos dicen a partir de qué tensión nos aseguran que tenemos un 1 o un 0 a la entrada o a la salida. Se pueden ver en forma de gráfico, para simplificarlo, empecemos con un 74LS04:

Ésto nos indica que a la entrada, lo que nosotros controlamos, si ponemos un rango de tensión de 0 a 0.8 voltios, el integrado seguro que lo capta como un LOW. Y lo mismo ocurre si ponemos, una tensión entre 2 y 5 voltios, el integrado seguro lo capta como HIGH. ¿Y por qué lo remarco? Porque ésto en realidad es cosa de estadística ¿Habéis visto el rango entre 0.8 y 2 voltios, el inaceptable? Supongamos que hemos elegido un integrado cualquiera, ponemos un regulador de tensión variable a la entrada y observamos cómo lo capta el integrado. Llegamos hasta 0.8 y subimos, quizás hasta 1 voltio no pase nada, 1.2, 1.4 … Quién sabe, el caso es que en un punto desconocido entre 0.8 y 2 voltios el integrado dejará de captar un 0 y captará un 1, pero no nos vamos a poner a mirar integrado por integrado cuál es éste punto (que además cambia por temperatura, humedad, calidad de alimentación, etc.), sino que hacemos una estadística y sacamos los márgenes. Es más un caso de asegurarse.

Y a la salida, cosa que no controlamos, obtendremos un rango de tensión que va entre 0 y 0.4 para un OUTPUT LOW y entre 2.4 y 5 voltios para un OUTPUT HIGH. Nos interesa éste dato para saber el margen de ruido, es decir, cuánto se puede mover la señal arriba o abajo para que el siguiente integrado de la cola lo capte bien y no se meta en zona “inaceptable”. Es cosa de restar:

- Margen de ruido HIGH: 2.4 – 2 V = 0.4V

- Margen de ruido LOW 0.8-0.4 = 0.4V

Importante para líneas que cojan ruido del ambiente o aparatos cercanos.

Para la tecnología CMOS ocurre algo similar, pero los márgenes son bastante más amplios, además de incluir en las datasheet varios en condición de la alimentación, ya que un integrado CMOS puro (no HCT), puede ser alimentado en rangos muy distintos de tensión, límites recomendados por el fabricante que podrían llegar a estar entre 1.2 y 15 voltios.

Así por ejemplo, con unos 5V de alimentación tendríamos HIGH con un input de 3.15 hasta Vcc y LOW entre 0 y 1.35V

En la salida tendríamos un HIGH con tensión mínima de 4.4V y un LOW con tensión máxima de 0.1V.

Otra cosa a tener en cuenta son los tiempos de retardo, es un pequeño tiempo que necesitan los transistores para polarizarse. Ésto hace que la reacción entre que se aplica una entrada y hay una salida no sea inmediata, sino que tarde un poco, aunque sean nanosegundos (del orden éste van las cosas). La tecnología TTL siempre ha sido más rápida que la CMOS, razón por la que se usa la familia HC (high speed CMOS), aunque hoy en día casi se podría decir lo contrario.

Control de entrada con botón y resistencia pull-up o pull-down

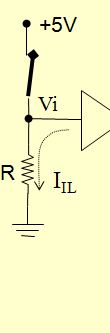

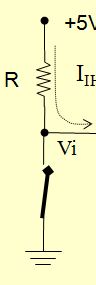

En muchos sistemas, sobre todo ya podéis haberlo visto en PICs y Arduinos, se utiliza un pequeño circuito de input con un botón y una resistencia, uno de ellos va a tierra y otro a alimentación. Si la resistencia va a masa, entonces la llamamos pull-down, y si va a alimentación es de pull-up. Entonces el circuito puede ir así:

Pero ojo, porque ésto nos trae otro dolor de cabeza. Tenemos que buscar el equilibrio entre resistencia-tensión LOW-corriente HIGH.

En el primer caso, hay que ponerle un valor a la resistencia de tal forma que cuando el interruptor esté abierto y queramos un LOW a la entrada, la corriente que se drena no aumente la tensión hasta V input HIGH y confunda al integrado. Por ejemplo en un TTL como el que ya hemos visto tendríamos un rango de resistencia con máximo de 0.8/0.0004 = 2k ohmios, pero no podemos ponerle el valor demasiado pequeño, porque entonces disiparía demasiada potencia, y el circuito consumiría muchísimo.

En el segundo caso, la resistencia debe ser lo suficientemente pequeña para dejar pasar la corriente mínima de polarización: 5/0.00002 = 250k ohmios máximo.

Entre otras maldades, podemos poner en la entrada un sensor de luz, basado en sólo una resistencia y un LDR, y calcular el divisor de tensión, dimensionando la resistencia para tener el margen necesario y que la puerta se active con cierto nivel de luz.

Existen puertas con histéresis que realmente, en la zona “inaceptable”, no cambian hasta llegar a los niveles máximos y mínimos. Éstas se usan para señales con mucho ruido, distorsionadas o que entran con defectos.